- 您现在的位置:买卖IC网 > Sheet目录316 > BR34E02FVT-WE2 (Rohm Semiconductor)IC EEPROM SPD 2KB I2C 8TSSOP

�� �

�

BR34E02FVT-W,� BR34E02NUX-W�

�Technical� Note�

�●� Data� transfer� on� the� I� C� BUS�

�2�

�○� Data� transfer� on� the� I� 2� C� BUS�

�The� BUS� is� considered� to� be� busy� after� the� START� condition� and� free� a� certain� time� after� the� STOP� condition.�

�Every� SDA� byte� must� be� 8-bits� long� and� requires� an� ACKNOWLEDGE� signal� after� each� byte.� The� devices� have� Master�

�and� Slave� configurations.� The� Master� device� initiates� and� ends� data� transfer� on� the� BUS� and� generates� the� clock� signals�

�in� order� to� permit� transfer.�

�The� EEPROM� in� a� slave� configuration� is� controlled� by� a� unique� address.� Devices� transmitting� data� are� referred� to� as� the�

�Transmitter.� The� devices� receiving� the� data� are� called� Receiver.�

�○� START� Condition� (Recognition� of� the� START� bit)�

�?� All� commands� are� proceeded� by� the� start� condition,� which� is� a� High� to� Low� transition� of� SDA� when� SCL� is� High.�

�?� The� device� continuously� monitors� the� SDA� and� SCL� lines� for� the� start� condition� and� will� not� respond� to� any� command�

�until� this� condition� has� been� met.� (See� Fig.1-(b)� START/STOP� Bit� Timing)�

�○� STOP� Condition� (Recognition� of� STOP� bit)�

�?� All� communications� must� be� terminated� by� a� stop� condition,� which� is� a� Low� to� High� transition� of� SDA� when� SCL� is� High.�

�(See� Fig.1-(b)� START/STOP� Bit� Timing)�

�○� Write� Protect� By� Soft� Ware�

�?� Set� Write� Protect� command� and� permanent� set� Write� Protect� command� set� data� of� 00h� ~� 7Fh� in� 256� words� write�

�protection� block.� Clear� Write� Protect� command� can� cancel� write� protection� block� which� is� set� by� set� write� Protect�

�command.� Cancel� of� write� protection� block� which� is� set� by� permanent� set� Write� Protect� command� at� once� is�

�impossibility.� When� these� commands� are� carried� out,� WP� pin� must� be� OPEN� or� GND.�

�○� Acknowledge�

�?� Acknowledge� is� a� software� used� to� indicate� successful� data� transfers.� The� Transmitter� device� will� release� the� BUS� after�

�transmitting� eight� bits.� When� inputting� the� slave� address� during� write� or� read� operation,� the� Transmitter� is� the� μ-COM.�

�When� outputting� the� data� during� read� operation,� the� Transmitter� is� the� EEPROM.�

�?� During� the� ninth� clock� cycle� the� Receiver� will� pull� the� SDA� line� Low� to� verify� that� the� eight� bits� of� data� have� been�

�received.� (When� inputting� the� slave� address� during� write� or� read� operation,� EEPROM� is� the� receiver.� When� outputting�

�the� data� during� read� operation� the� receiver� is� the� μ-COM.)�

�?� The� device� will� respond� with� an� Acknowledge� after� recognition� of� a� START� condition� and� its� slave� address� (8bit).�

�?� In� WRITE� mode,� the� device� will� respond� with� an� Acknowledge� after� the� receipt� of� each� subsequent� 8-bit� word� (word�

�address� and� write� data).�

�?� In� READ� mode,� the� device� will� transmit� eight� bits� of� data,� release� the� SDA� line,� and� monitor� the� line� for� an� Acknowledge.�

�?� If� an� Acknowledge� is� detected� and� no� STOP� condition� is� generated� by� the� Master,� the� device� will� continue� to� transmit�

�the� data.� If� an� Acknowledge� is� not� detected,� the� device� will� terminate� further� data� transmissions� and� await� a� STOP�

�condition� before� returning� to� standby� mode.�

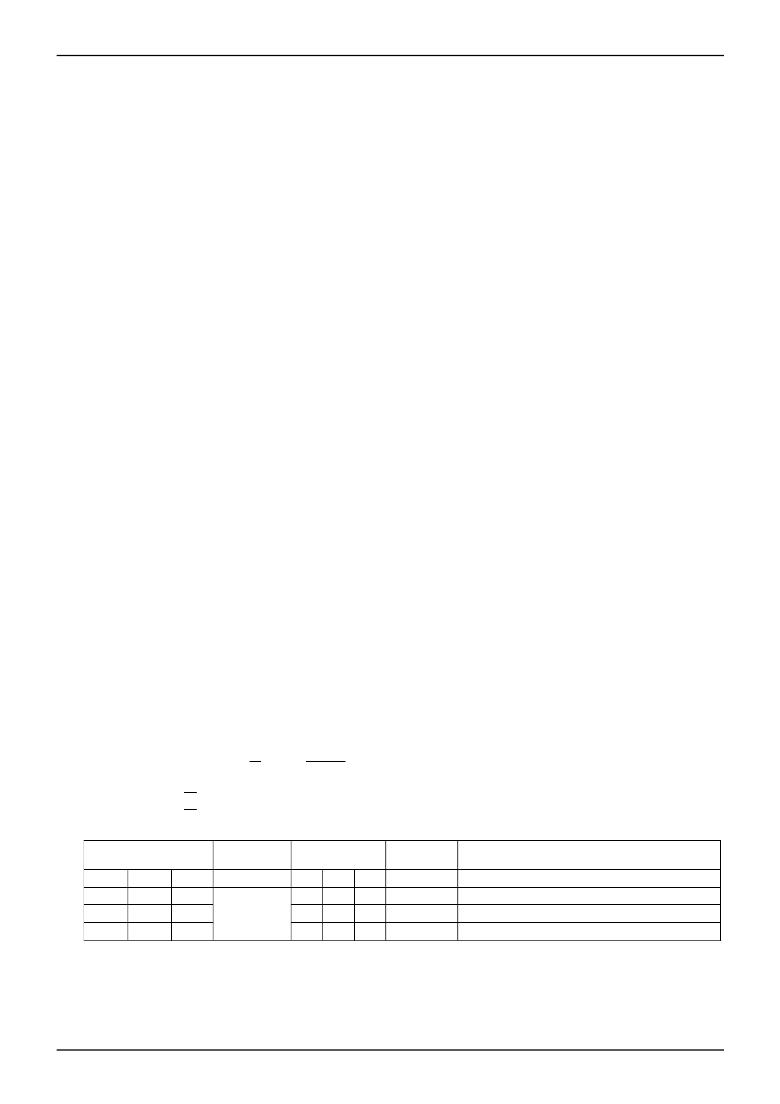

�○� Device� Addressing�

�?� Following� a� START� condition,� the� Master� outputs� the� Slave� address� to� be� accessed.� The� most� significant� four� bits� of� the�

�slave� address� are� the� “device� type� indentifier.”� For� this� EEPROM� it� is� “1010.�

�”� (For� WP� register� access� this� code� is� "0110".)�

�?� The� next� three� bits� identify� the� specified� device� on� the� BUS� (device� address).�

�The� device� address� is� defined� by� the� state� of� the� A0,A1� and� A2� input� pins.� This� IC� works� only� when� the� device� address�

�input� from� the� SDA� pin� corresponds� to� the� status� of� the� A0,A1� and� A2� input� pins.� Using� this� address� scheme� allows� up�

�to� eight� devices� to� be� connected� to� the� BUS.�

�?� The� last� bit� of� the� stream� (R/W� …� READ/WRITE)� determines� the� operation� to� be� performed.�

�R/W=0�

�R/W=1�

�????�

�????�

�WRITE� (including� word� address� input� of� Random� Read)�

�READ�

�Slave� Address� Set� Pin�

�A2� A1� A0�

�A2� A1� A0�

�GND� GND� VHV�

�GND� Vcc� VHV�

�Device� Type�

�1010�

�0110�

�Device� Address�

�A2� A1� A0�

�A2� A1� A0�

�0� 0� 1�

�0� 1� 1�

�Read� Write�

�Mode�

�―�

�R/W�

�―�

�R/W�

�―�

�R/W�

�―�

�R/W�

�Access� Area�

�2kbit� Access� to� Memory�

�Access� to� Permanent� Set� Write� Protect� Memory�

�Access� to� Set� Write� Protect� Memroy�

�Access� to� Clear� Write� Protect� MEmory�

�www.rohm.com�

�?� 2009� ROHM� Co.,� Ltd.� All� rights� reserved.�

�7/18�

�2009.09� -� Rev.B�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

BR34L02FV-WE2

IC EEPROM 2KBIT 400KHZ 8SSOP

BR93L76RFVJ-WE2

IC EEPROM 8KBIT 2MHZ 8TSSOP

BS08D-112

TRIGGER BILTRL SW 175MA TO-92

BU04P-TZ-S

TZ CONN 4 POS SINGLE ROW

BU9829GUL-WE2

IC EEPROM 16KBIT SPI 9VCSP

BU9832GUL-WE2

IC EEPROM 8KBIT SPI VCSP50L2 TR

BU9833GUL-WE2

IC EEPROM 2KBIT 100KHZ VCSP50L1

BU9844GUL-WE2

IC EEPROM 16KBIT 2WIRE VCSP50L1

相关代理商/技术参数

BR34E02FVT-WTR

制造商:ROHM 制造商全称:Rohm 功能描述:DDR/DDR2 (For memory module) SPD Memory

BR34E02NUX-3E2

制造商:ROHM 制造商全称:Rohm 功能描述:Serial EEPROM Series Standard EEPROM Plug & Play EEPROM

BR34E02NUX-3TR

制造商:ROHM 制造商全称:Rohm 功能描述:Serial EEPROM Series Standard EEPROM Plug & Play EEPROM

BR34E02NUX-W

制造商:ROHM Semiconductor 功能描述:

BR34E02NUX-WE2

制造商:ROHM 制造商全称:Rohm 功能描述:DDR/DDR2 (For memory module) SPD Memory

BR34E02NUX-WTR

功能描述:电可擦除可编程只读存储器 电可擦除可编程只读存储器 Serial-2Wire 2Kb

RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

BR34E02NUX-WTTR

制造商:ROHM Semiconductor 功能描述:EEPROM SERIAL-2WIRE 2K-BIT 256 X 8 1.8V/2.5V/3.3V 8-PIN VSON - Tape and Reel

BR34E02-W

制造商:ROHM 制造商全称:Rohm 功能描述:DDR/DDR2 (For memory module) SPD Memory